7A Constant On Time Synchronous Buck Regulator with I2C Production

#### **Features**

- Pseudo frequency COT control

- Extremely fast line/load transient response

- I<sup>2</sup>C for output adjustment (3.4 Mbps)

- 1.2 MHz switching frequency I<sup>2</sup>C Interface

- Extremely low-R<sub>DSON</sub> MOSFETS

- Input voltage rail 2.7V to 6V

- Up to 7A output current

- Power save mode for light-load efficiency

- UVLO, OVP, and OCP

- -40°C to 85°C ambient temperature

- Available in QFN 2mm x 3mm 14 package

- RoHS compliant

### **General Description**

The APW7438 is a digitally controlled step-down regulator IC with an integrated  $20m\Omega$  high-side P-channel MOSFET and an  $8m\Omega$  low-side N-channel MOSFET.

It features ANPEC's proprietary COT-mode control scheme for near-instantaneous correction to line/load transients for a voltage range of 2.7V to 6V, and 7A with constant frequency.

The APW7438 is equipped with an automatic PFM/PWM mode operation. At light load, the IC operates in the PFM mode to reduce the switching losses and provides high efficiency over light to heavy loads with loading-modulated frequency.

The APW7438 has an I<sup>2</sup>C serial interface port for output voltage margining and monitoring, if required (it can also operate in default mode).

In addition it includes robust fault monitoring functions.

The APW7438 is available in 0.9V default output voltage (no voltage divider is necessary) which can be changed from 0x01 Register.

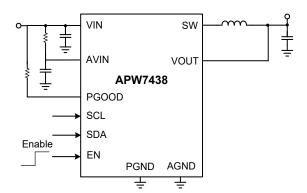

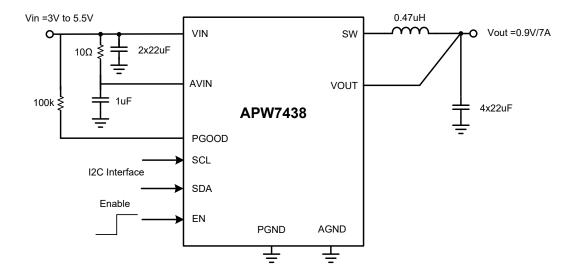

## **Simplified Application Circuit**

## **Applications**

- High performance hard disk drive (HDD)

- Solid-state drive

- Data center applications

- Raid/host bus adaptors

- Optical transceivers

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

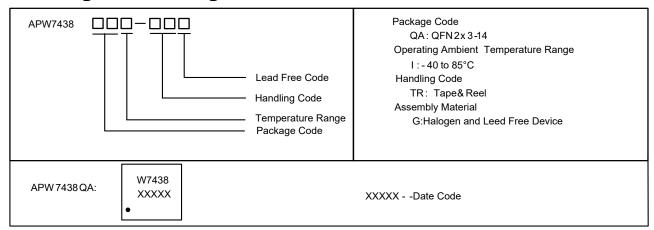

## **Ordering and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature. ANPEC defines "Green" to mean lead-free (RoHS compliant) and halogen free (Br or Cl does not exceed 900ppm by weight in homogeneous material and total of Br and Cl does not exceed 1500ppm by weight).

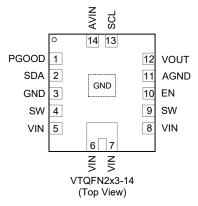

## **Pin Configuration**

## **Absolute Maximum Ratings** (Note 1)

| Symbol           | Parameter                                       | Rating    | Unit |

|------------------|-------------------------------------------------|-----------|------|

| $V_{\text{VIN}}$ | VIN, SW to GND                                  | -0.3 ~ 7  | V    |

| $V_{sw}$         | SW to GND (shorter than 50 ns)                  | -2 ~ 7    | V    |

| Other Pins       | AVIN, VOUT, SDA, SCL, EN, PGOOD to GND          | -0.3 ~ 7  | V    |

| T <sub>J</sub>   | Maximum Junction Temperature                    | 150       | °C   |

| T <sub>STG</sub> | Storage Temperature                             | -65 ~ 150 | °C   |

| T <sub>SDR</sub> | Maximum Lead Soldering Temperature (10 Seconds) | 260       | °C   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Thermal Characteristics**

| Symbol               | Parameter                                           | Typical Value |    |      |

|----------------------|-----------------------------------------------------|---------------|----|------|

| $\theta_{JA}$        | Junction-to-Ambient Resistance in free air (Note 2) | QFN2x3-14     | 49 | °C/W |

| $\theta_{\text{JC}}$ | Junction-to-Case Resistance in free air (Note 2)    |               | 20 | °C/W |

Note 2:  $\theta_{JA}$  and  $\theta_{JC}$  is measured with the component mounted on a high effective thermal conductivity test board in free air.

## **Recommended Operating Conditions** (Note 3)

| Symbol           | Parameter                | Range     | Unit |

|------------------|--------------------------|-----------|------|

| V <sub>VIN</sub> | VIN to GND Voltage       | 2.7 ~ 6   | V    |

| I <sub>OUT</sub> | Converter Output Current | 0 ~ 7     | Α    |

| T <sub>A</sub>   | Ambient Temperature      | -40 ~ 85  | °C   |

| T <sub>J</sub>   | Junction Temperature     | -40 ~ 125 | °C   |

Note 3: Refer to the typical application circuit.

## **Electrical Characteristics**

Test Condition:  $V_{VIN}$ =2.7 ~ 6V,  $T_A$ = -40 to 85°C. Typical values are at  $T_A$ =25°C.

| Symbol             | Parameter                                | Test Conditions                                           |         | APW7438 | Unit    |       |

|--------------------|------------------------------------------|-----------------------------------------------------------|---------|---------|---------|-------|

| Зуньон             | Parameter                                | lest conditions                                           | Min.    | Тур.    | Max.    | Oill  |

| Input Voltag       | e                                        |                                                           |         |         |         |       |

| Ι <sub>Q</sub>     | Input current                            | ILOAD=0, PSM enabled                                      | 60      | 100     | 160     | μА    |

|                    | V Chutdown Cumply Current                | EN=GND, T <sub>A</sub> =25°C                              | -       | 0.1     | 1.2     | μА    |

| I <sub>VIN</sub>   | V <sub>VIN</sub> Shutdown Supply Current | EN=GND, T <sub>A</sub> = -40 ~ 85°C                       | -       | 0.1     | 6.5     | μА    |

| UVLO               | Under voltage rising threshold           | VIN rising                                                | 2.3     | 2.55    | 2.65    | V     |

| UVLO<br>HYST       | UVLO hysteresis                          |                                                           | 0.1     | 0.15    | 0.22    | V     |

| OVPR               | Over voltage rising threshold            |                                                           | 6       | 6.2     | 6.4     | V     |

| OVPF               | Over voltage falling hysteresis          |                                                           | 0.1     | 0.2     | 0.3     | V     |

| VREF               |                                          |                                                           |         |         |         | ,     |

| TSS                | Softstart time                           | From VOUT 0% ~ 90% of VREF                                | 0.65    | 1       | 1.35    | ms    |

| TSS2               | VREF slew rate                           | SLEW: Ctrl2(3:2)=01                                       | 4.5     | 8       | 10      | mV/μs |

| THICCUP            | Hiccup time                              | VOUT=0.2V                                                 | -       | 9.8     | -       | ms    |

| t <sub>D(ON)</sub> | Turn On Delay Time                       | From being enabled to SW start switching                  | 1.15    | -       | 1.95    | ms    |

| Output Volta       | age                                      |                                                           |         |         |         |       |

| VOUT               | Default VOUT                             | VOUT=0.9V, (VIN=2.7V – 5V),<br>VSEL=[6:0]0111100          | 891     | 900     | 909     | mV    |

|                    | VOUT I2C VSEL                            | VOUT=0.75V, (VIN=2.7V – 5V),<br>VSEL=[6:0]0011110         | 738.75  | 750     | 761.25  | mV    |

|                    |                                          | VOUT=1.195V, (VIN=2.7V – 5V),<br>VSEL=[6:0]1110111        | 1177.08 | 1195    | 1212.93 | mV    |

|                    | Line regulation                          | VIN from 3V to 5.5V, ILOAD=1A <sup>1</sup>                | -       | 0.1     | -       | %     |

|                    | Load regulation                          | ILOAD=0A to 5A1                                           | -       | 0.23    | -       | %     |

|                    | VOUT input current                       |                                                           | -       | 0       | 0.2     | μА    |

| UVP                | VOUT under voltage threshold             | VOUT below this threshold will initiate a hiccup sequence | 79      | 82      | 85      | %VREF |

# **APW7438**

## **Electrical Characteristics (Cont.)**

Test Condition:  $V_{VIN}$ =2.7 ~ 6V,  $T_A$ = -40 to 85°C. Typical values are at  $T_A$ =25°C.

| Symbol           | Parameter                   | Test Conditions                   |      | APW743 | Unit    |         |

|------------------|-----------------------------|-----------------------------------|------|--------|---------|---------|

| Syllibol         | raiailletei                 | rest conditions                   | Min. | Тур.   | Max.    | O I III |

| Switch (SW)      |                             |                                   | '    | 1      |         |         |

| RDSON_H          | High side on resistance     | VIN=5V                            | 10   | 20     | 32.5    | mΩ      |

| RDSON_L          | Low side on resistance      | VIN=5V                            | 4    | 8      | 12.9    | mΩ      |

| OCP              | Current limit               |                                   | 7.5  | 10     | 12.5    | Α       |

| T <sub>OTR</sub> | Thermal shut down threshold |                                   | -    | 150    | -       | °C      |

|                  | Hysteresis                  |                                   | -    | 40     | -       | °C      |

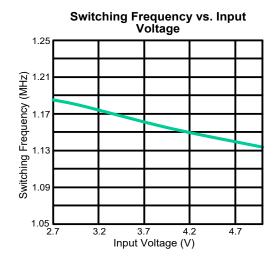

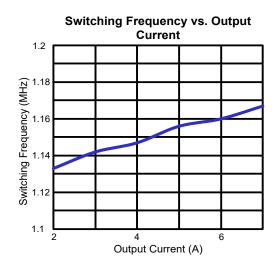

| F <sub>sw</sub>  | Switching Frequency         |                                   | 1    | 1.2    | 1.4     | MHz     |

| RSWDISC          | SW discharge resistance     | EN=low; Discharge: Ctrl3(0)=1     | 170  | 200    | 270     | Ω       |

| EN               |                             |                                   | ,    |        |         |         |

| V <sub>IH</sub>  | Input high                  |                                   | 1.1  | -      | -       | V       |

| V <sub>IL</sub>  | Input low                   |                                   | -    | -      | 0.4     | V       |

|                  | Input current               |                                   | -    | 0      | 1       | μА      |

| PGOOD            |                             |                                   |      |        |         |         |

| V <sub>POK</sub> | PGOOD VOUT lower threshold  | VOUT rising, percentage of VREF   | 85   | 90     | 95      | %VREF   |

|                  | PGOOD VOUT upper threshold  | VOUT falling, percentage of VREF  | 105  | 110    | 115     | %VREF   |

|                  | Hysteresis                  | Percentage of VREF 5%             | 2    | 5      | 7       | %VREF   |

|                  | PGOOD pull down resistance  |                                   | 6    | 13     | 25      | Ω       |

|                  | PGOOD leakage current       |                                   | -    | 0      | 0.2     | μА      |

|                  | PGOOD delay                 | PGOOD rising edge delay           | -    | 45     | -       | ms      |

| 7 Bit DAC        |                             |                                   |      |        |         |         |

|                  | Differential linearity      | Monotonicity assured by design    | -    | -      | 0.8     | LSB     |

| SDA and SC       | L                           |                                   |      |        |         |         |

| V <sub>IH</sub>  | Input high                  |                                   | 1.2  | -      | -       | V       |

| V <sub>IL</sub>  | Input low                   |                                   | -    | -      | 0.4     | V       |

|                  | Input current               |                                   | -    | 0      | 0.2     | μА      |

| VOL              | Low level output voltage    | Logic0 output voltage, Isink=2mA¹ | 0    | -      | 0.2*VDD | V       |

| IOL              | Low level output current    | VOL=0.4V <sup>1</sup>             | 3    | -      | -       | mA      |

## **Typical Operating Characteristics**

## **Operating Waveforms**

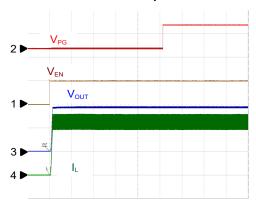

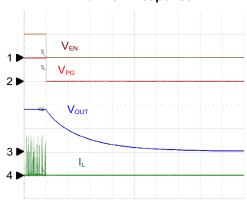

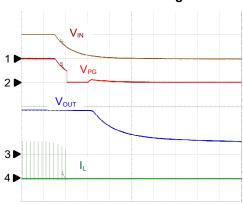

#### **Turn On Response**

$\begin{array}{l} \text{CH1:V}_{\text{EN}}\text{,}5\text{V/Div, DC} \\ \text{CH2:V}_{\text{PG}}\text{,}5\text{V/Div, DC} \\ \text{CH3:V}_{\text{OUT}}\text{,}500\text{mV/Div, DC} \\ \text{CH4:I}_{\text{L}}\text{,}2\text{A/Div, DC} \\ \text{TIME:}10\text{ms/Div} \end{array}$

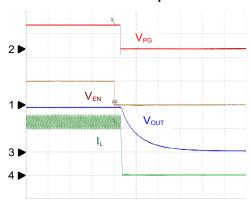

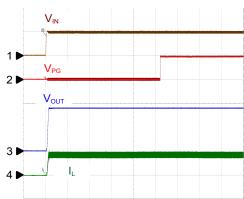

#### Turn Off Response

$\begin{array}{l} \text{CH1:V}_{\text{EN}}, 5\text{V/Div, DC} \\ \text{CH2:V}_{\text{PG}}, 5\text{V/Div, DC} \\ \text{CH3:V}_{\text{OUT}}, 500\text{mV/Div, DC} \\ \text{CH4:I}_{\text{L}}, 2\text{A/Div, DC} \\ \text{TIME:} 20 \mu\text{s/Div} \end{array}$

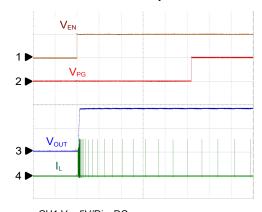

#### **Turn On Response**

$\begin{array}{l} \text{CH1:V}_{\text{EN}}\text{,}5\text{V/Div}\text{, DC} \\ \text{CH2:V}_{\text{PG}}\text{,}5\text{V/Div}\text{, DC} \\ \text{CH3:V}_{\text{OUT}}\text{,}500\text{mV/Div}\text{, DC} \\ \text{CH4:I}_{\text{L}}\text{,}500\text{mA/Div}\text{, DC} \\ \text{TIME:}10\text{ms/Div} \end{array}$

#### **Turn Off Response**

$\begin{array}{l} \text{CH1:V}_{\text{EN}}\text{,}5\text{V/Div, DC} \\ \text{CH2:V}_{\text{PG}}\text{,}5\text{V/Div, DC} \\ \text{CH3:V}_{\text{OUT,}}\text{,}500\text{mV/Div, DC} \\ \text{CH4:I}_{\text{L}}\text{,}500\text{mA/Div, DC} \\ \text{TIME:5s/Div} \end{array}$

## **Operating Waveforms (Cont.)**

$\begin{array}{l} \text{CH1:V}_{\text{IN}}, \text{5V/Div}, \, \text{DC} \\ \text{CH2:V}_{\text{PG}}, \text{5V/Div}, \, \text{DC} \\ \text{CH3:V}_{\text{OUT}}, \text{500mV/Div}, \, \text{DC} \\ \text{CH4:I}_{\text{L}}, \text{5A/Div}, \, \text{DC} \\ \text{TIME:10ms/Div} \end{array}$

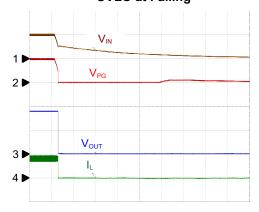

### **UVLO** at Falling

$\begin{array}{l} \text{CH1:V}_{\text{IN}}, \text{5V/Div}, \, \text{DC} \\ \text{CH2:V}_{\text{PG}}, \text{5V/Div}, \, \text{DC} \\ \text{CH3:V}_{\text{OUT}}, \text{500mV/Div}, \, \text{DC} \\ \text{CH4:I}_{\text{L}}, \text{5A/Div}, \, \text{DC} \\ \text{TIME:50ms/Div} \end{array}$

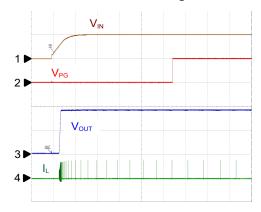

#### **UVLO** at Rising

$\begin{array}{l} \text{CH1:V}_{\text{IN}}, \text{5V/Div}, \, \text{DC} \\ \text{CH2:V}_{\text{PG}}, \text{5V/Div}, \, \text{DC} \\ \text{CH3:V}_{\text{OUT}}, \text{500mV/Div}, \, \text{DC} \\ \text{CH4:I}_{\text{L}}, \text{1A/Div}, \, \text{DC} \\ \text{TIME:10ms/Div} \end{array}$

#### **UVLO at Falling**

$\begin{array}{l} \text{CH1:V}_{\text{IN}}, 5\text{V/Div}, \, \text{DC} \\ \text{CH2:V}_{\text{PG}}, 5\text{V/Div}, \, \text{DC} \\ \text{CH3:V}_{\text{OUT}}, 500\text{mV/Div}, \, \text{DC} \\ \text{CH4:I}_{\text{L}}, 500\text{mA/Div}, \, \text{DC} \\ \text{TIME:} 50\text{ms/Div} \end{array}$

## **Operating Waveforms (Cont.)**

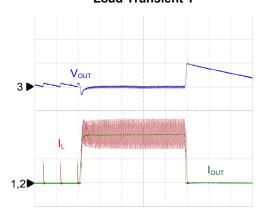

### Load Transient 1

CH1: $I_{OUT}$ ,1A/Div, DC CH2: $I_L$ ,1A/Div, DC CH3: $V_{OUT}$ ,50mV/Div, AC TIME:20 $\mu$ s/Div

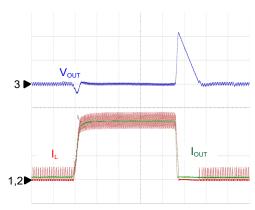

#### **Load Transient 2**

CH1: $I_{OUT}$ ,2A/Div, DC CH2: $I_{L}$ ,2A/Div, DC CH3: $V_{OUT}$ ,50mV/Div, AC TIME:20 $\mu$ s/Div

## **Pin Descriptions**

| Р              | IN    |                                                                                                                                                                                                                                         |

|----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN            | NAME  | Function                                                                                                                                                                                                                                |

| NO.            | NAME  |                                                                                                                                                                                                                                         |

| 1              | PGOOD | Open drain status output, requires external pull-up resistor. This pin goes low, when VOUT exceeds the defined power good range.                                                                                                        |

| 2              | SDA   | Serial data bus (bidirectional) for I <sup>2</sup> C. Connect directly to GND, if unused.                                                                                                                                               |

| 3              | GND   | Ground. Connect to ground plane.                                                                                                                                                                                                        |

| 4, 9           | SW    | Switching node. Drives the external L-C low pass filter.                                                                                                                                                                                |

| 5, 6,<br>7, 8  | VIN   | Input of IC and buck stage. Connect to input rail VIN (between 2.7V and 6V). A minimum input capacitance of one $1\mu$ F and one $22\mu$ F of X5R or a multilayer ceramic, should be placed very close to IC between this node and GND. |

| 10             | EN    | Enable for switching regulator. Force high to enable, force low to disable the IC.                                                                                                                                                      |

| 11             | AGND  | Analog ground. Connect to ground plane.                                                                                                                                                                                                 |

| 12             | VOUT  | Output voltage sense. Connect directly to output rail or resistive voltage divider output.                                                                                                                                              |

| 13             | SCL   | Serial clock input for I <sup>2</sup> C. Connect directly to GND, if unused.                                                                                                                                                            |

| 14             | AVIN  | Analog VIN voltage input pin.                                                                                                                                                                                                           |

| Exposed<br>Pad | GND   | Ground. Connect to ground plane.                                                                                                                                                                                                        |

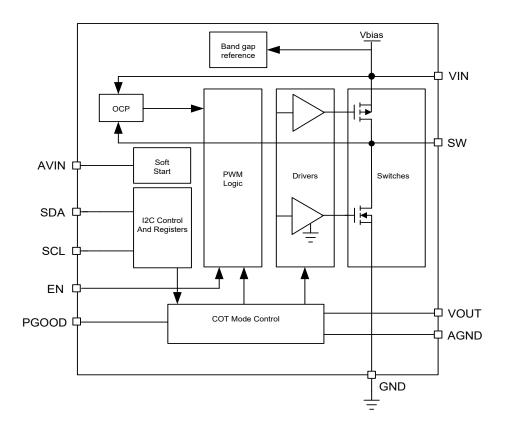

## **Block Diagram**

# **Typical Application Circuit**

## I<sup>2</sup>C Programming

#### I<sup>2</sup>C SERIAL CONTROL INTERFACE

The APW7438 has a bidirectional I²C interface that compatible with the I²C (Inter IC) bus protocol and supports standard mode (100-kHz), fast mode (400-kHz) and the high-speed mode (up to 3.4Mbps in wire mode) data transfer rates for single byte write and read operations. This is a slave only device that does not support a multi-master bus environment or wait state insertion. The control interface is used to program the registers of the device and to read device status. The APW7438 supports the standard-mode I²C bus operation (100 kHz maximum), the fast I²C bus operation (400 kHz maximum) and the high-speed mode (up to 3.4Mbps in wire mode). The APW7438 performs all I²C operations without I²C wait cycles.

#### General I<sup>2</sup>C Operation

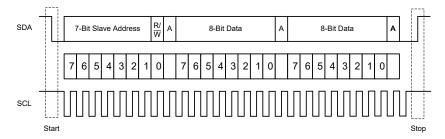

The I<sup>2</sup>C bus uses two signals; SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially one bit at a time. The address and data can be transferred in byte (8-bit) format, with the most significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus.

The bus uses transitions on the data pin (SDA) while the clock is high to indicate a start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data bit transitions must occur within the low time of the clock period. These conditions are shown in Figure 1. The master generates the 7-bit slave address and the  $R\overline{W}$  bit — a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ) to open communication with another device and then waits for an acknowledge condition. The APW7438 holds SDA low during the acknowledge clock period to indicate an acknowledgment. When this occurs, the master transmits the next byte of the sequence.

Each device is addressed by a unique 7-bit slave address plus  $R\overline{W}$  bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the high level for the bus.

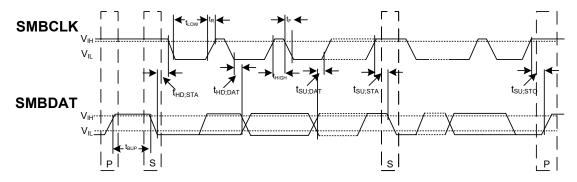

Figure 1. Typical I<sup>2</sup>C sequence

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 1. The APW7438 I<sup>2</sup>C Slave Address is a hard-coded 7-bit address "0010010" (12H).

#### Single-Byte Transfer

The serial control interface supports single-byte R/W operations for sub-addresses 0x00 to 0xFF.

Supplying a sub-address for each sub-address transaction is referred to as random I<sup>2</sup>C addressing. The APW7438 also supports sequential I<sup>2</sup>C addressing. For write transactions, if a sub-address is issued followed by data for that sub-address and the 15 sub-addresses that follow, a sequential I<sup>2</sup>C write transaction has taken place, and the data for all 16 sub-addresses is successfully received by the APW7438. For I<sup>2</sup>C sequential write transactions, the sub-address then serves as the start address, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines how many sub-addresses are written. As was true for random addressing, sequential addressing requires that a complete set of data be transmitted. If only a partial set of data is written to the last sub-address, the data for the last sub-address is discarded. However, all other data written is accepted; only the incomplete data is discarded.

## I<sup>2</sup>C Programming (Cont.)

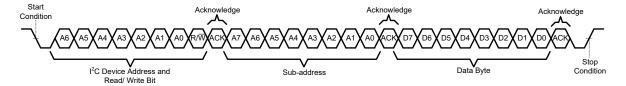

### Single-Byte Write

As shown in Figure 2, a single-byte data write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the R/W bit. The R/W bit determines the direction of the data transfer. For a write data transfer, the R/W bit will be a 0. After receiving the correct I<sup>2</sup>C device address and the R/W bit, the APW7438 responds with an acknowledge bit. Next, the master transmits the address byte or bytes corresponding to the APW7438 internal memory address being accessed. After receiving the address byte, the APW7438 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the APW7438 again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data write transfer.

Figure 2. Single-Byte Write Transfer

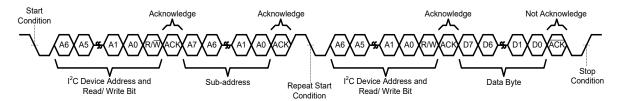

#### Single-Byte Read

As shown in Figure 3, a single-byte data read transfer begins with the master device transmitting a start condition followed by the  $I^2C$  device address and the R/W bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte or bytes of the internal memory address to be read. As a result, the R/W bit becomes a 0. After receiving the APW7438 address and the R/W bit, APW7438 responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the APW7438 address and the R/W bit again. This time the R/W bit becomes a 1, indicating a read transfer. After receiving the address and the R/W bit, the APW7438 again responds with an acknowledge bit. Next, the APW7438 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not acknowledge followed by a stop condition to complete the single byte data read transfer.

Figure 3. Single-Byte Read Transfer

# I<sup>2</sup>C Programming (Cont.)

| SMBus Co             | ntrol Timing                                   |                                                                       |            |      |             |     |

|----------------------|------------------------------------------------|-----------------------------------------------------------------------|------------|------|-------------|-----|

|                      | SMBDAT and SMBCLK Leakage<br>Current           |                                                                       | -          | 0.01 | 1           | μА  |

| F <sub>SMB</sub>     | SMBus Operating Frequency                      |                                                                       | -          | -    | 100<br>400  | KHz |

| $T_{BUF}$            | Bus free time between stop and start condition | SCL=100KHz<br>SCL=400KHz                                              | 4.7<br>1.3 | -    | -           | μs  |

| T_ <sub>HD_STA</sub> | Hold time after start condition                | After this period, the first clock is generated SCL=100KHz SCL=400KHz | 4<br>0.6   | -    | -           | μS  |

| T_ <sub>SU_STA</sub> | Repeated start condition setup time            | SCL=100KHz<br>SCL=400KHz                                              | 4.7<br>0.6 | -    | -           | μS  |

| T_ <sub>SU_STO</sub> | Stop condition setup time                      | SCL=100KHz<br>SCL=400KHz                                              | 4<br>0.6   | -    | -           | μS  |

| T_ <sub>HD_DAT</sub> | Data hold time                                 | SCL=100KHz<br>SCL=400KHz                                              | 300<br>300 | -    | -           | ns  |

| T_ <sub>SU_DAT</sub> | Data setup time                                | SCL=100KHz<br>SCL=400KHz                                              | 250<br>100 | -    | -           | ns  |

| T_ <sub>LOW</sub>    | Clock low period                               | SCL=100KHz<br>SCL=400KHz                                              | 4.7<br>1.3 | -    | -           | μS  |

| T_ <sub>HIGH</sub>   | Clock high period                              | SCL=100KHz<br>SCL=400KHz                                              | 4<br>0.6   | -    | -           | μS  |

| $T_{F\_SMB}$         | Fall time of SMB DAT/CLK                       | SCL=100KHz<br>SCL=400KHz                                              | -          | -    | 300<br>300  | ns  |

| $T_{R\_SMB}$         | Rise time of SMB DAT/CLK                       | SCL=100KHz<br>SCL=400KHz                                              | -          | -    | 1000<br>300 | ns  |

| Сь                   | Capacitive Load for Each B <sub>µ</sub> s Line | SCL=100KHz<br>SCL=400KHz                                              | -          | -    | 400<br>400  | pF  |

### **Timing Diagram**

Figure 4: SMBus Common AC Specification

## **Register Map**

| Address | Name             | Default Value |

|---------|------------------|---------------|

| 00h     | Status           | 44            |

| 01h     | V <sub>SEL</sub> | BC            |

| 02h     | Ctrl1            | 80            |

| 03h     | Ctrl2            | 05            |

| 04h     | Vender           | 10            |

| 05h     | Die              | 02            |

| 06h     | Ctrl3            | 02            |

### **REG00 Status Register**

| Data Bit         | D7                             | D6                                       | D5                | D4        | D3                | D2            | D1   | D0  |

|------------------|--------------------------------|------------------------------------------|-------------------|-----------|-------------------|---------------|------|-----|

| Bit Name         | ILIM                           | UVLO                                     | VIN_OVP           | VOUT_OVP  | VOUT_UVP          | PG            | OTW  | OTP |

| Read/Write       | R                              | R                                        | R                 | R         | R                 | R             | R    | R   |

| Power On Default | 0                              | 1                                        | 0                 | 0         | 0                 | 1             | 0    | 0   |

| Bit Name         |                                |                                          |                   | Bit De    | finition          |               |      |     |

| ILIM             |                                |                                          | urrent limit cond |           | FET is greater th | an OCP thresh | old. |     |

| UVLO             | UVLO=1, VIN ><br>UVLO=0, VIN < |                                          |                   |           |                   |               |      |     |

| VIN_OVP          | Latched to 1 if                | a VIN OVP ever                           | nt occurs         |           |                   |               |      |     |

| VOUT_OVP         | Latched to 1 if                | a VOUT OV eve                            | ent occurs        |           |                   |               |      |     |

| VOUT_UVP         | Latch to 1 if the              | VOUT under v                             | oltage is reache  | d         |                   |               |      |     |

| PG               | Indicate if PMI                | C output is ready                        | (PG=1), otherv    | vise PG=0 |                   |               |      |     |

| OTW              |                                | OTW=1, TEMP > 130°<br>OTW=0, TEMP < 130° |                   |           |                   |               |      |     |

| OTP              | Latch to 1 if the              | over temperatu                           | ire is reached    |           |                   |               |      |     |

### REG01 V<sub>SEL</sub> Register

| Data Bit               | D7                             | D6                                                                                                                                                              | D5                     | D4     | D3       | D2 | D1 | D0 |  |  |

|------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------|----------|----|----|----|--|--|

| Bit Name               | EN                             |                                                                                                                                                                 | V <sub>SEL</sub> [6:0] |        |          |    |    |    |  |  |

| Read/Write             | R/W                            |                                                                                                                                                                 |                        |        | R/W      |    |    |    |  |  |

| Power On Default       | 1                              | 0                                                                                                                                                               | 1                      | 1      | 1        | 1  | 0  | 0  |  |  |

| Bit Name               |                                |                                                                                                                                                                 |                        | Bit De | finition |    |    |    |  |  |

| EN                     | EN=0 Device d<br>EN=1 Device e |                                                                                                                                                                 |                        |        |          |    |    |    |  |  |

| V <sub>SEL</sub> [6:0] |                                | -bit DAC value to set VREF. The default value is determined by the part ordering code. 000000: FB=0.6V, 0000001: 0.605V 0111100: 0.9V (Default) 1111111: 1.235V |                        |        |          |    |    |    |  |  |

### **REG02 Ctrl1 Register**

| Data Bit         | D7                                                                                   | D6        | D5 | D4     | D3       | D2   | D1 | D0   |

|------------------|--------------------------------------------------------------------------------------|-----------|----|--------|----------|------|----|------|

| Bit Name         | FREQ[2:0]                                                                            |           |    |        | Res      | erve |    | MODE |

| Read/Write       | R/W R/W R/W R                                                                        |           |    |        | R        | R    | R  | R/W  |

| Power On Default | 1                                                                                    | 0         | 0  | 0      | 0        | 0    | 0  | 0    |

| Bit Name         |                                                                                      |           |    | Bit De | finition |      |    |      |

| FREQ[2:0]        | 000: 2.2Mhz<br>001: 1.8Mhz<br>010: 1.5Mhz<br>100: 1.2Mhz<br>101: 1Mhz<br>110: 0.8Mhz | (Default) |    |        |          |      |    |      |

| MODE             | 0: Auto PFM<br>1: PWM mod                                                            |           |    |        |          |      |    |      |

## Register Map (Cont.)

### **REG03 Ctrl2 Register**

| Data Bit         | D7                                                    | D6            | D5               | D4             | D3             | D2            | D1      | D0     |

|------------------|-------------------------------------------------------|---------------|------------------|----------------|----------------|---------------|---------|--------|

| Bit Name         | Reserve                                               |               |                  |                | SLEW_F         | RATE[1:0]     | PG_CTRL | PG_SET |

| Read/Write       | R                                                     | R R R R/W R/W |                  |                |                |               | R/W     | R/W    |

| Power On Default | 0                                                     | 0             | 0                | 0              | 0              | 1             | 0       | 1      |

| Bit Name         |                                                       |               |                  | Bit De         | finition       |               |         |        |

| SLEW_RATE[1:0]   | 00: 32mV/us<br>01: 8mV/us<br>10: 4mV/us<br>11: 2mV/us |               |                  |                |                |               |         |        |

| PG_CTRL          | 0: enable PG<br>1: disable PG                         |               |                  |                |                |               |         |        |

| PG_SET           | When PG CT                                            | RL is 1, PG p | in is pulled hig | h if PG Set is | 0; otherwise p | ull down PG p | pin     |        |

### **REG04 Vendor ID Register**

| Data Bit         | D7              | D6             | D5 | D4       | D3 | D2 | D1 | D0 |

|------------------|-----------------|----------------|----|----------|----|----|----|----|

| Bit Name         | VID[3:0] DIE_ID |                |    | VID[3:0] |    |    |    |    |

| Read/Write       |                 | R              |    |          |    |    |    |    |

| Power On Default | 0               | 0 0 0 1 0 0    |    |          |    | 0  |    |    |

| Bit Name         |                 | Bit Definition |    |          |    |    |    |    |

### **REG05 DIE Register**

| Data Bit         | D7             | D6      | D5 | D4 | D3 | D2      | D1 | D0 |

|------------------|----------------|---------|----|----|----|---------|----|----|

| Bit Name         |                | Reserve |    |    |    | Die_Rev |    |    |

| Read/Write       | R              | R       | R  | R  | R  |         |    |    |

| Power On Default | 0              | 0       | 0  | 0  | 0  | 0       | 1  | 1  |

| Bit Name         | Bit Definition |         |    |    |    |         |    |    |

### **REG06 Ctrl3 Register**

| Data Bit         | D7                                                                                                     | D6                                                                                         | D5  | D4       | D3       | D2      | D1      | D0        |

|------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|----------|----------|---------|---------|-----------|

| Bit Name         | Reserve                                                                                                | Reserve SS[1:0]                                                                            |     | VOUTOV_L | VINOV_L  | SW_RATE | DLY_DIS | DISCHARGE |

| Read/Write       | R                                                                                                      | R/W                                                                                        | R/W | R/W      | R/W      | R/W     | R/W     | R/W       |

| Power On Default | 0                                                                                                      | 0                                                                                          | 0   | 0        | 0        | 0       | 1       | 0         |

| Bit Name         |                                                                                                        |                                                                                            |     | Bit Det  | finition |         |         |           |

| SS               | Set Buckx Softstart Time 00: 1.0ms 01: 0.5ms 10: 0.25ms 11: 0.125ms                                    |                                                                                            |     |          |          |         |         |           |

| VOUTOV_L         |                                                                                                        | 1: VOUTOVP Latch 0: VOUTOVP non_latch                                                      |     |          |          |         |         |           |

| VINOVP_L         |                                                                                                        | 1: VINOVP Latch 0: VINOVP non_latch                                                        |     |          |          |         |         |           |

| SW_RATE          | 0: High switch                                                                                         | Switch node rise rate 0: High switch node rise rate 1: Low switch node rise rate (20% Off) |     |          |          |         |         |           |

| DLY_DIS          | 0: No PGOOD delay 1: 45mSec PGOOD delay enable                                                         |                                                                                            |     |          |          |         |         |           |

| Discharge        | 0: No discharge 1: When the regulator is disabled, the output voltage is discharged through the SW pin |                                                                                            |     |          |          |         |         |           |

15

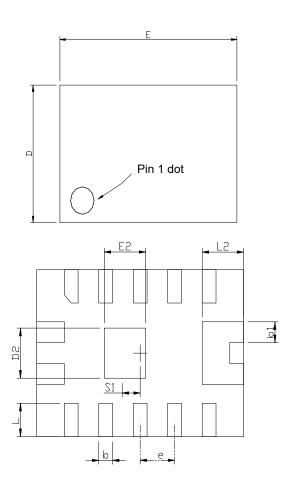

# **Package Information**

QFN2x3-14

| S      |        | Q FN2  | x3-14 |        |

|--------|--------|--------|-------|--------|

| M<br>B | MILLIN | METERS | INC   | CHES   |

| O<br>L | MIN.   | MAX.   | MIN.  | MAX.   |

| Α      | 0.80   | 0.90   | 0.031 | 0.035  |

| A1     | 0.00   | 0.05   | 0.000 | 0.002  |

| А3     | 0.20   | ) REF  | 0.00  | )8 REF |

| b      | 0.15   | 0.25   | 0.006 | 0.010  |

| b1     | 0.20   | 0.30   | 0.008 | 0.012  |

| D      | 1.90   | 2.10   | 0.075 | 0.083  |

| Е      | 2.90   | 3.10   | 0.114 | 0.122  |

| D2     | 0.50   | 0.70   | 0.020 | 0.028  |

| E2     | 0.50   | 0.70   | 0.020 | 0.028  |

| е      | 0.50   | ) BSC  | 0.02  | 20 BSC |

| L      | 0.35   | 0.45   | 0.014 | 0.018  |

| L1     | 0.55   | 0.65   | 0.022 | 0.026  |

| S1     | 0.21   | 0.31   | 0.008 | 0.012  |

| aaa    | 0.0    | 08     | 0.0   | 003    |

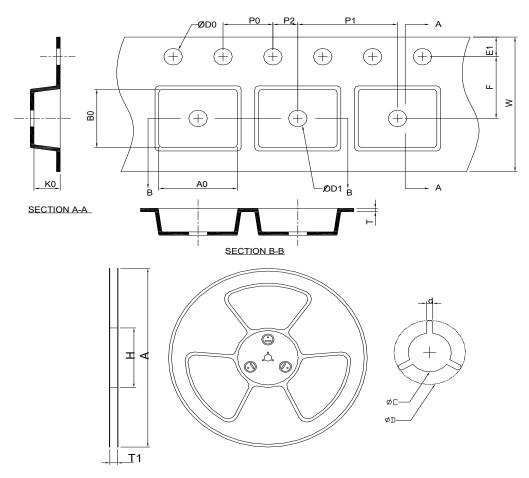

# **Carrier Tape & Reel Dimensions**

| Application | Α          | н        | T1                 | С                  | d        | D                 | W         | E1        | F         |

|-------------|------------|----------|--------------------|--------------------|----------|-------------------|-----------|-----------|-----------|

|             | 178.0±2.00 | 50 MIN.  | 16.5+2.00<br>-0.00 | 13.0+0.50<br>-0.20 | 1.5 MIN. | 20.2 MIN.         | 12.0±0.20 | 1.75±0.10 | 5.5±0.05  |

| QFN(2x3)    | P0         | P1       | P2                 | D0                 | D1       | Т                 | A0        | В0        | K0        |

|             | 4.0±0.10   | 4.0±0.10 | 2.0±0.05           | 1.5+0.10<br>-0.00  | 1.5 MIN. | 0.6+0.00<br>-0.40 | 2.20±0.20 | 3.20±0.20 | 1.30±0.20 |

(mm)

# **Devices Per Unit**

| Package type | Packing     | Quantity |  |

|--------------|-------------|----------|--|

| QFN(2x3)     | Tape & Reel | 3000     |  |

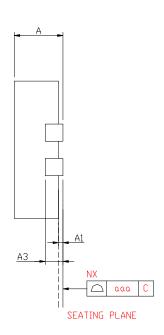

# **Taping Direction Information**

QFN2x3-14

## **Classification Profile**

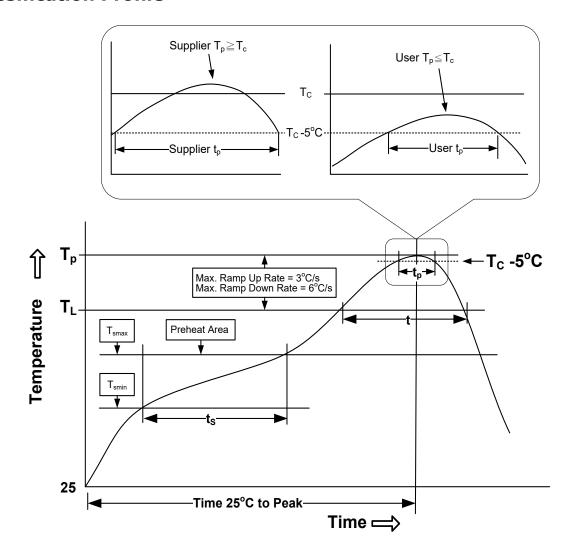

### **Classification Reflow Profiles**

| Profile Feature                                                                                                                                                                                           | Sn-Pb Eutectic Assembly            | Pb-Free Assembly                   |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|--|

| $\begin{tabular}{lll} \textbf{Preheat & Soak} \\ \textbf{Temperature min } (T_{smin}) \\ \textbf{Temperature max } (T_{smax}) \\ \textbf{Time } (T_{smin} \text{ to } T_{smax}) \ (t_s) \\ \end{tabular}$ | 100°C<br>150°C<br>60-120 seconds   | 150°C<br>200°C<br>60-120 seconds   |  |

| Average ramp-up rate $(T_{smax} \text{ to } T_P)$                                                                                                                                                         | 3°C/second max.                    | 3°C/second max.                    |  |

| Liquidous temperature (T <sub>L</sub> )<br>Time at liquidous (t <sub>L</sub> )                                                                                                                            | 183°C<br>60-150 seconds            | 217°C<br>60-150 seconds            |  |

| Peak package body Temperature (T <sub>p</sub> )*                                                                                                                                                          | See Classification Temp in table 1 | See Classification Temp in table 2 |  |

| Time (t <sub>P</sub> )** within 5°C of the specified classification temperature (T <sub>c</sub> )                                                                                                         | 20** seconds                       | 30** seconds                       |  |

| Average ramp-down rate (T <sub>p</sub> to T <sub>smax</sub> )                                                                                                                                             | 6°C/second max.                    | 6°C/second max.                    |  |

| Time 25°C to peak temperature                                                                                                                                                                             | 6 minutes max.                     | 8 minutes max.                     |  |

<sup>\*</sup> Tolerance for peak profile Temperature (T<sub>o</sub>) is defined as a supplier minimum and a user maximum.

Note: ANPEC's green products meet or exceed the lead-free requirements of IPC/JEDEC J-STD-020D for MSL classification at lead-free peak reflow temperature.

Table 1. SnPb Eutectic Process – Classification Temperatures (Tc)

| Package   | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------|------------------------|------------------------|

| Thickness | <350                   | ≥350                   |

| <2.5 mm   | 235°C                  | 220°C                  |

| ≥2.5 mm   | 220°C                  | 220°C                  |

Table 2. Pb-free Process – Classification Temperatures (Tc)

| Package         | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> | Volume mm <sup>3</sup> |

|-----------------|------------------------|------------------------|------------------------|

| Thickness       | <350                   | 350-2000               | >2000                  |

| <1.6 mm         | 260°C                  | 260°C                  | 260°C                  |

| 1.6 mm – 2.5 mm | 260°C                  | 250°C                  | 245°C                  |

| ≥2.5 mm         | 250°C                  | 245°C                  | 245°C                  |

### **Reliability Test Program**

| Test item     | Method             | Description                            |

|---------------|--------------------|----------------------------------------|

| SOLDERABILITY | JESD-22, B102      | 5 Sec, 245°C                           |

| HOLT          | JESD-22, A108      | 1000 Hrs, Bias @ T <sub>j</sub> =125°C |

| PCT           | JESD-22, A102      | 168 Hrs, 100%RH, 2atm, 121°C           |

| TCT           | JESD-22, A104      | 500 Cycles, -65°C~150°C                |

| НВМ           | MIL-STD-883-3015.7 | $VHBM \ge 2KV$                         |

| MM            | JESD-22, A115      | VMM ≥ 200V                             |

| Latch-Up      | JESD 78            | 10ms, $1_{tr} \ge 100$ mA              |

|               |                    |                                        |

<sup>\*\*</sup> Tolerance for time at peak profile temperature (tp) is defined as a supplier minimum and a user maximum.

# **APW7438**

### **Customer Service**

**Anpec Electronics Corp.**

Head Office:

No.6, Duxing 1st Rd., East Dist., Hsinchu City 300096, Taiwan (R.O.C.)

Tel: 886-3-5642000 Fax: 886-3-5642050

Taipei Branch:

2F, No.11, Ln. 218, Sec. 2, Zhongxing Rd., Xindian Dist., New Taipei City 231037, Taiwan (R.O.C.)

Tel: 886-2-2910-3838 Fax: 886-2-2917-3838